Introduction to XC6SLX45-2CSG484I and Optimization Principles

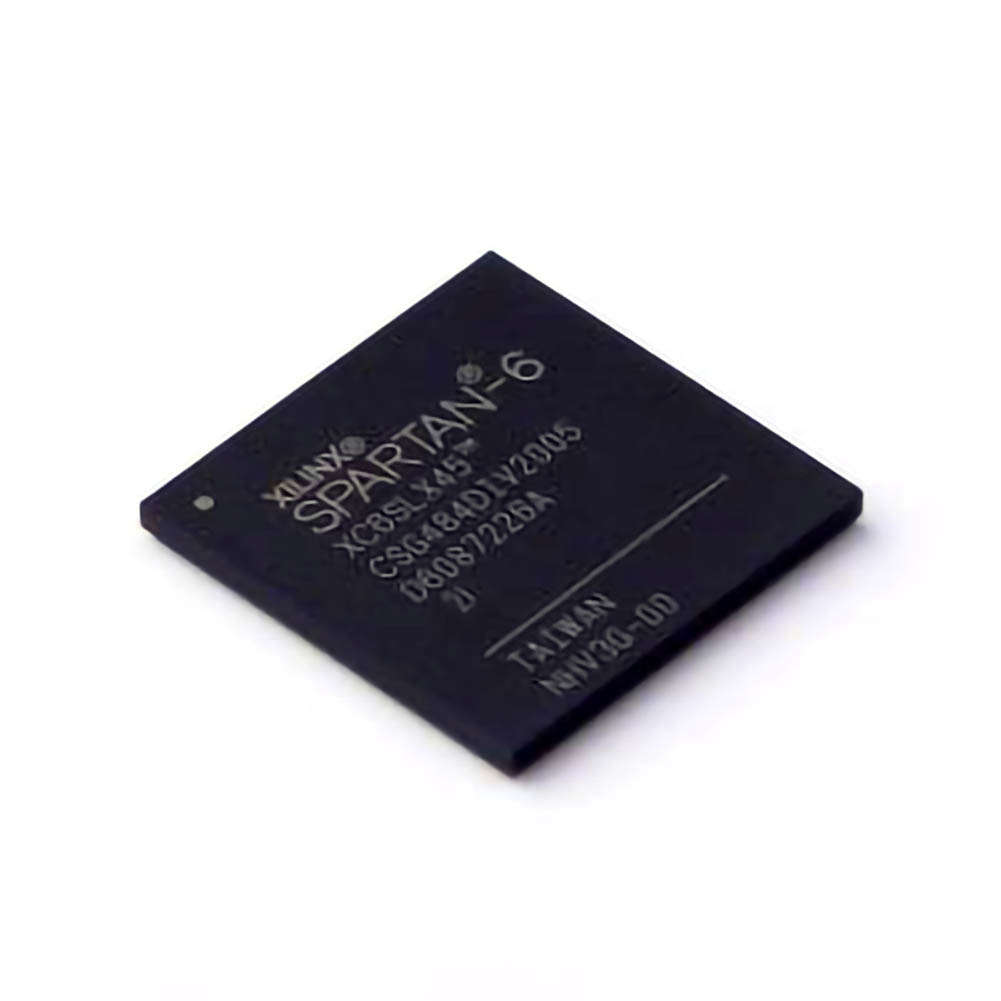

The XC6SLX45-2CSG484I, part of the Xilinx Spartan-6 family, is a Power ful mid-range Field-Programmable Gate Array ( FPGA ) suitable for a wide range of applications, from consumer electronics to automotive and industrial systems. With 45,000 logic cells and a vast array of I/O resources, this FPGA strikes a balance between performance, flexibility, and cost, making it ideal for medium-sized FPGA projects. However, achieving optimal performance in FPGA design requires careful attention to several factors such as resource utilization, power consumption, and Timing constraints.

In this article, we will explore practical optimization strategies for maximizing the capabilities of the XC6SLX45-2CSG484I in mid-sized FPGA designs. These strategies will focus on optimizing performance, minimizing power consumption, and ensuring efficient utilization of resources, all while adhering to project timelines and constraints.

Understanding the XC6SLX45-2CSG484I FPGA

Before diving into optimization techniques, it’s essential to have a clear understanding of the core features and capabilities of the XC6SLX45-2CSG484I. This FPGA belongs to the Xilinx Spartan-6 family, known for its low-cost and high-performance architecture. The XC6SLX45-2CSG484I provides the following features:

45,000 Logic Cells: A sufficient number of logic cells to handle medium-scale digital designs with plenty of flexibility.

Up to 192 I/O Pins: Multiple I/O options for communication with external devices or integration into larger systems.

Dedicated DSP Slices: High-performance DSP blocks for fast arithmetic operations, ideal for signal processing applications.

Block RAM: Built-in Memory for storing data and performing various processing tasks.

Advanced Clock Management : Features such as Phase-Locked Loops ( PLLs ) for optimizing clock distribution and reducing jitter.

Low Power Consumption: One of the standout features of Spartan-6 FPGAs, designed to meet the power needs of battery-operated or thermal-sensitive applications.

These features make the XC6SLX45-2CSG484I a versatile choice for a wide array of projects, including communications, Video Processing , automotive, and more. However, to fully exploit these capabilities, design optimization is a crucial step in any FPGA development cycle.

Key Optimization Goals

When optimizing FPGA designs for the XC6SLX45-2CSG484I, the primary goals typically include:

Performance Optimization: Achieving the highest possible operational speed while meeting timing constraints.

Power Optimization: Reducing power consumption without sacrificing performance or functionality, critical for portable or embedded systems.

Resource Utilization: Efficiently using the available logic elements, memory, and DSP slices to meet the design's functional requirements.

Optimization Techniques for the XC6SLX45-2CSG484I

1. Clock Domain Management and Timing Constraints

Efficient clock domain management is essential for achieving optimal performance in FPGA designs. The XC6SLX45-2CSG484I supports multiple clocking resources, including PLLs and global clocks, which can be used to distribute clocks efficiently across the FPGA fabric.

To optimize timing, you should ensure that:

Clock Domain Crossing (CDC): Properly manage CDC to avoid timing issues between different clock domains. Use synchronization techniques such as dual-flop synchronizers or FIFO buffers to handle asynchronous data transfers safely.

Clock Constraints: Set accurate clock constraints in the design files to ensure that the FPGA tools can properly optimize timing paths.

Timing Closure: Perform timing analysis and apply optimizations such as pipelining, retiming, and resource sharing to meet timing constraints.

2. Resource Sharing and Pipelining for Performance

One of the most effective ways to optimize FPGA designs for performance is through resource sharing and pipelining. These techniques help maximize throughput while minimizing resource usage.

Resource Sharing: In cases where multiple operations use the same hardware resources, consider sharing resources to reduce the overall logic usage. This can be achieved by combining operations in a single shared hardware block, but care should be taken to ensure that the sharing does not create timing or resource contention issues.

Pipelining: Implementing pipelines in critical data paths can dramatically increase throughput. By breaking a long combinatorial path into smaller stages, each of which can be processed in parallel, you can improve the speed of your design without needing to increase the clock frequency. For example, DSP-heavy applications like filtering or FFTs can benefit from deep pipelining.

3. Power Optimization Techniques

Power consumption is a critical factor in FPGA design, especially for embedded systems and portable devices. The Spartan-6 family of FPGAs, including the XC6SLX45-2CSG484I, provides several techniques to minimize power usage:

Clock Gating: Disable clocks to unused or idle logic blocks to save power. Use clock gating techniques to turn off portions of the FPGA when they are not in use.

Power-aware Synthesis: Use power-aware synthesis tools provided by Xilinx, such as Vivado or ISE, which can optimize the design for lower power usage by selecting lower-power configurations for logic elements and memory.

Dynamic Voltage and Frequency Scaling (DVFS): If your application allows for it, adjust the FPGA’s operating frequency and voltage to suit the power requirements. For example, reducing the clock frequency in less-demanding sections of the design can save significant power.

4. Utilizing Block RAM Efficiently

The XC6SLX45-2CSG484I includes a large amount of Block RAM (BRAM), which can be a valuable resource for optimizing your design. Efficient use of BRAM can not only reduce the need for external memory but also improve overall performance.

Memory Hierarchy: Implement a memory hierarchy in your design to make use of on-chip BRAM for faster data access. Use BRAM for frequently accessed data, and offload less critical data to external memory.

Data Width Optimization: Minimize the width of data stored in BRAM whenever possible. Smaller data widths can lead to reduced resource usage and potentially lower power consumption.

5. Efficient I/O Handling

Optimizing the FPGA’s I/O operations is another critical aspect of design optimization. The XC6SLX45-2CSG484I supports a wide range of I/O standards, including LVDS, LVCMOS, and others, which can be tailored for your specific application.

I/O Pin Mapping: Ensure efficient use of I/O pins by carefully mapping critical signals to faster or more capable I/O pins. This can reduce routing congestion and improve signal integrity.

I/O Clocking: Use external clocking and phase-locked loops (PLLs) to synchronize high-speed I/O signals, which is especially important in designs involving high-frequency communication protocols like Gigabit Ethernet or high-speed video interface s.

Advanced FPGA Design Techniques and Case Studies

6. Case Study 1: Video Processing Optimization

Consider a mid-sized FPGA design targeting high-definition video processing. The design needs to capture video, process it in real time, and output it to a display or other output device.

Pipelining: To handle the large volume of video data, pipelining is essential. Each stage of the video processing pipeline—such as filtering, scaling, and color space conversion—can be implemented as a separate stage in the pipeline. This reduces the processing time for each frame and increases overall throughput.

Block RAM Utilization: The video frames are stored temporarily in BRAM, which provides faster access compared to external memory. The design also employs dual-port BRAM to read and write frames simultaneously.

Clock Management: Video processing often involves different clock rates for capturing, processing, and displaying video. PLLs are used to synchronize the clock domains for efficient operation.

By employing these techniques, the design maximizes the performance of the XC6SLX45-2CSG484I, ensuring smooth video processing with minimal latency.

7. Case Study 2: Digital Signal Processing (DSP) Optimization

For a digital signal processing application, such as a software-defined radio (SDR), the XC6SLX45-2CSG484I’s DSP slices can be fully leveraged to perform fast arithmetic operations like filtering, FFT, and modulation.

DSP Slice Utilization: The design uses multiple DSP slices to parallelize operations such as filtering and FFT. This enables the design to handle high-speed signal processing tasks with minimal delay.

Power Optimization: To optimize power consumption, unused DSP slices are disabled when not required, and clock gating is used to reduce unnecessary activity in the logic blocks.

Clock Domain Crossing: Efficient handling of clock domains is crucial in SDR designs, where different sections of the system operate at different frequencies. CDC techniques like FIFO buffers and synchronizers ensure safe data transfer across clock domains.

These optimizations ensure that the SDR system operates efficiently while meeting both performance and power requirements.

8. Final Thoughts on Optimization Design for XC6SLX45-2CSG484I

Optimizing FPGA designs for the XC6SLX45-2CSG484I requires a comprehensive approach that addresses key concerns like timing, power consumption, resource utilization, and design complexity. By using the techniques discussed in this article—such as clock domain management, resource sharing, pipelining, and efficient memory usage—engineers can achieve high-performance, low-power designs that make full use of the capabilities of this versatile FPGA.

As FPGA technology continues to evolve, the tools and techniques for optimization will also advance, but the fundamental principles of resource management, performance tuning, and power reduction will remain critical for successful FPGA development.

Partnering with an electronic components supplier sets your team up for success, ensuring the design, production, and procurement processes are quality and error-free.