Understanding Configuration Errors in EP3C25E144I7N FPGA

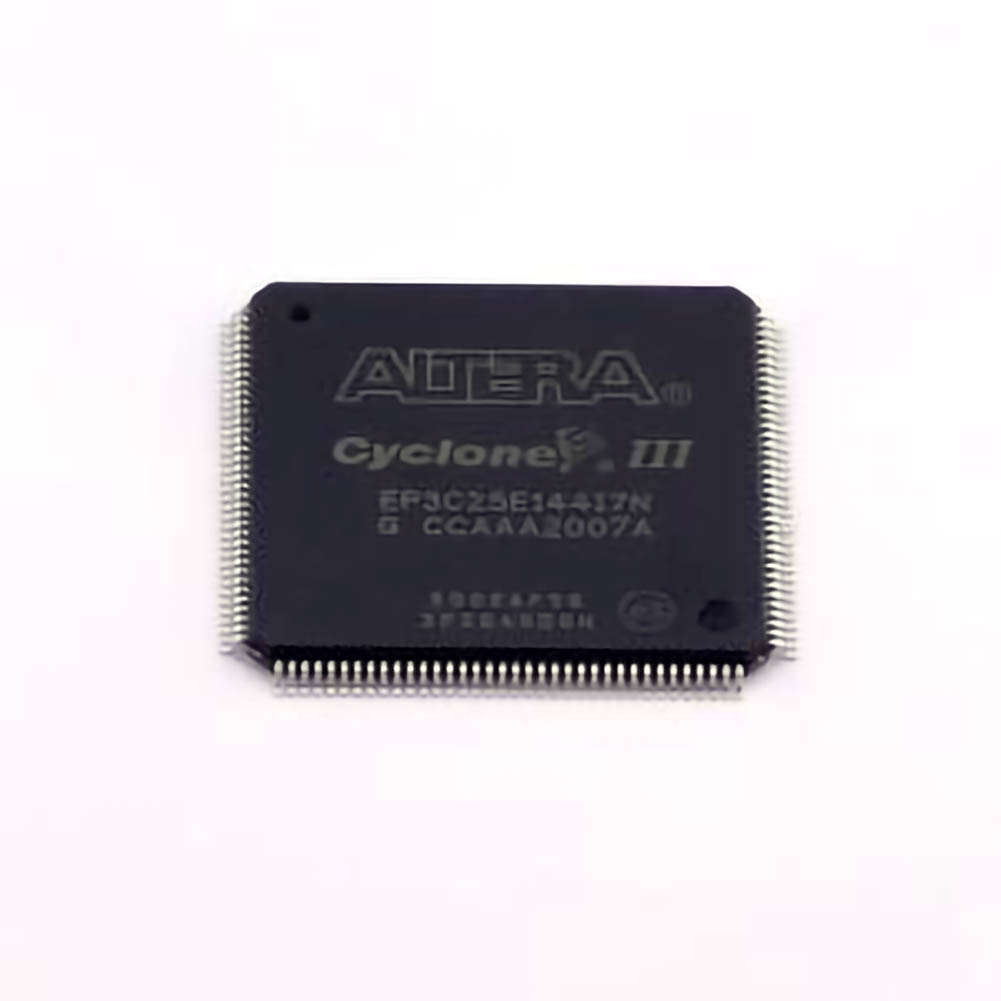

FPGAs (Field-Programmable Gate Arrays) are widely used in industries such as telecommunications, automotive, consumer electronics, and aerospace for their flexibility and performance. The EP3C25E144I7N FPGA from Intel (formerly Altera) is one of the popular choices for designers looking for a mid-range solution that balances performance, Power efficiency, and cost. However, like any advanced hardware component, the EP3C25E144I7N FPGA comes with its own set of configuration challenges that designers may encounter during development.

Whether you're a beginner or an experienced FPGA designer, understanding common configuration errors and their solutions can help speed up your development process and prevent costly mistakes.

1. Incorrect Pin Assignments

Pin assignments are critical to FPGA design, as they define how the FPGA connects to external components such as sensors, Memory , and other devices. One of the most frequent configuration errors is an incorrect pin assignment, which occurs when a designer mistakenly assigns a signal to the wrong pin.

Solution:

To avoid pin assignment errors, always double-check the pin assignments in your FPGA design files (such as the .qsf file for Intel FPGAs). Utilize the pin planning tools available in the FPGA development environment, such as Intel Quartus Prime, to visually map out pin locations and ensure they align with your schematic. Also, use the FPGA’s documentation and pinout diagrams as references.

2. Mismatched Voltage Levels

FPGA configuration errors can also stem from mismatched voltage levels between the FPGA and external components. Many FPGAs, including the EP3C25E144I7N, require specific voltage levels for configuration, which may differ from other components in the system.

Solution:

Ensure that the voltage levels for both the FPGA and external devices are correctly set according to the FPGA datasheet. The EP3C25E144I7N typically operates with a core voltage of 1.2V or 1.8V, and different I/O banks may have varying voltage requirements. Double-check the voltage levels for the external devices, and if necessary, use level shifters to align the voltage levels of the FPGA’s I/O pins with those of the other components.

3. Incorrect Configuration File Format

FPGA configuration files are the blueprint that tells the FPGA how to configure itself. The most common configuration file formats for Intel FPGAs are the .sof (SRAM Object File) and .pof (Programming Object File). If the wrong file format is used, the FPGA will fail to configure properly.

Solution:

Make sure you generate the correct configuration file format using Intel Quartus Prime. If you are using an SRAM-based FPGA like the EP3C25E144I7N, you should typically use a .sof file for configuration. If you are configuring the FPGA in a non-volatile memory (such as flash memory), you may need to use a .pof file.

You can generate the appropriate configuration files by selecting the correct programming option during the compilation process in Quartus Prime.

4. JTAG Connection Issues

JTAG (Joint Test Action Group) is the most common method for programming and debugging FPGAs. Incorrect JTAG connections can cause configuration errors, preventing the FPGA from being programmed. A weak or improperly configured JTAG connection can also result in a failure to load the configuration file.

Solution:

Ensure that the JTAG programmer is correctly connected to both the FPGA and the computer. Verify that the cable is securely connected and that the drivers for the JTAG programmer are properly installed. In some cases, using a different USB port or trying a different JTAG programmer may help resolve connection issues. Also, verify the settings in Quartus Prime to ensure that the correct JTAG chain is selected.

5. Timing Violations During Configuration

Another common error is when timing violations occur during configuration. This typically happens if the design has not been properly timed, leading to setup or hold violations that prevent the FPGA from being correctly configured.

Solution:

In Quartus Prime, use the time analyzer to identify any timing violations in the design. Timing constraints must be carefully defined in the design files to ensure that the FPGA operates within the specified timing limits. If violations are found, refine your constraints or optimize the design to resolve the issues. Additionally, consider using timing closure tools in Quartus Prime to assist in fixing these violations.

6. Improper Clock Configuration

Clock configuration is another critical aspect of FPGA design. The EP3C25E144I7N supports multiple clock sources and configurations, but an improper clock setup can lead to incorrect behavior during configuration and operation.

Solution:

Double-check your clock assignments in the FPGA design, and make sure that the clock sources are correctly configured. If you're using external clock sources, verify that they are stable and connected to the correct pins. In some cases, a clock buffering issue could also cause timing problems, so make sure the clock networks are properly routed.

7. Faulty Configuration Voltage Supply

The configuration of FPGAs like the EP3C25E144I7N is heavily reliant on a stable voltage supply. If the voltage supply for the FPGA’s configuration pins is unstable or insufficient, configuration errors can occur.

Solution:

Ensure that the power supply for the FPGA is stable and meets the required specifications. This includes both the core voltage and the I/O voltage levels. Use a regulated power supply to avoid fluctuations. In some cases, the use of capacitor s close to the FPGA’s power pins can help reduce noise and ensure a stable configuration process.

8. Inadequate Reset Signal

A correct reset signal is necessary for proper FPGA configuration. If the reset signal is improperly driven or not provided at all, the FPGA may fail to load the configuration.

Solution:

Check the reset signal configuration and ensure that it is correctly implemented in the design. Ensure that the reset signal is active at the right moment during the configuration process and that it is applied to all necessary parts of the FPGA’s configuration logic. Many FPGAs, including the EP3C25E144I7N, require a specific reset sequence to begin configuration, so follow the guidelines provided in the datasheet and configuration manual.

Advanced Solutions for EP3C25E144I7N FPGA Configuration Errors

As you delve deeper into FPGA design with the EP3C25E144I7N, you may encounter more complex configuration issues. This section will address some of the advanced solutions to help you troubleshoot and resolve these errors.

9. Configuration Failure Due to Overheating

Overheating can affect the FPGA’s ability to configure correctly, especially during prolonged programming sessions or when the device is being used in a high-power environment.

Solution:

Ensure that the FPGA is operating within its thermal limits. The EP3C25E144I7N has specific temperature requirements, typically ranging from 0°C to 85°C for commercial-grade devices. Use a heat sink or fan if necessary to keep the FPGA cool during operation. Additionally, ensure that the FPGA’s environment is adequately ventilated, especially in high-performance or compact systems.

10. Corrupted Configuration Files

Configuration files can sometimes become corrupted, especially during a failed programming session or when transferred between different environments. Corrupted files can cause configuration errors or even make the FPGA non-responsive.

Solution:

Always verify the integrity of the configuration file before programming the FPGA. Intel Quartus Prime provides checksum utilities to verify that the configuration file is not corrupted. If the configuration file is corrupted, regenerate it from your source code. In some cases, it may be helpful to perform a "recovery" on the FPGA by using the appropriate software tools to reset its state.

11. Incompatible Firmware Versions

In some cases, the version of the firmware on the FPGA programmer or the development software may not be compatible with the FPGA hardware, leading to configuration errors.

Solution:

Ensure that the firmware on your FPGA programmer is up to date and compatible with the EP3C25E144I7N FPGA. Likewise, ensure that you are using the latest version of Intel Quartus Prime for compatibility with your FPGA device. Firmware updates can typically be downloaded from the manufacturer’s website, and these updates may contain bug fixes or performance improvements that could resolve configuration issues.

12. Power-on Reset Issues

Sometimes, the FPGA may not reset correctly on power-up, leading to configuration failure. This issue can occur if the power-up sequence is not properly timed or if external components are affecting the FPGA’s reset behavior.

Solution:

Use an external reset controller to manage the FPGA’s reset behavior during power-on. Ensure that the reset signal is asserted for a sufficient amount of time during power-up to allow the FPGA to initialize. Also, check the timing requirements for the reset signal in the EP3C25E144I7N datasheet to ensure it meets the necessary specifications.

13. Faulty External Configuration Memory

For non-volatile configurations, external memory (such as flash memory) is used to store the FPGA configuration bitstream. If the external memory is faulty, misconfigured, or incompatible, the FPGA may fail to load its configuration.

Solution:

Verify the health and compatibility of the external memory. Make sure that the memory is properly programmed with the configuration file, and that the interface between the FPGA and memory is correctly configured. Use the memory programming tools provided by Intel or third-party vendors to ensure the memory is programmed correctly.

14. Configuring via FPGA-embedded NIOS Processor

Some designs incorporate an embedded NIOS processor to handle configuration and other control tasks. Incorrect configuration of the NIOS processor or improper initialization can lead to issues with the FPGA configuration.

Solution:

Carefully review the NIOS processor's configuration in the design, paying particular attention to its boot sequence and memory initialization. The NIOS processor should be configured to load the configuration bitstream from the correct source (such as flash memory or a JTAG interface). If necessary, refer to Intel’s NIOS processor documentation for specific initialization steps.

Conclusion

Successfully configuring the EP3C25E144I7N FPGA requires careful attention to detail and a systematic approach to troubleshooting. By understanding the common errors and applying the solutions outlined in this article, you can improve your chances of a successful configuration and streamline your FPGA design process. As with any advanced hardware project, patience, thorough testing, and leveraging the right development tools are essential for overcoming configuration challenges and achieving a reliable and efficient design.

If you are looking for more information on commonly used Electronic Components Models or about Electronic Components Product Catalog datasheets, compile all purchasing and CAD information into one place.